The modern electronic warfare environment is becoming more and more complex, the signals are becoming denser, new systems of radars are constantly appearing, and the parameters of radar signals change in various rules. Therefore, sorting and identifying various new systems of radar signals from the dense and complex signal environment becomes electronic. A major problem in signal processing. In order to meet the needs of electronic support measures (ESM) for real-time signal sorting, higher requirements are put forward on the processing time of the processor: not only the hardware structure of the processor is required to have a good design and continuous optimization space, but also the device is required to have High integration, these have become factors that cannot be ignored. After in-depth analysis and research on related devices, this paper uses high-speed field programmable gate array devices (FPGA) to replace small and medium-sized integrated chips to design three-parameter correlation comparators, thereby realizing the design of pre-sorting devices.

1 Principle of signal pre-sorting based on associated comparatorCorrelation comparator technology has positive and important significance for hardware pre-sorting in high-density signal environments. The idea of ​​correlated comparators for signal pre-sorting originates from the radiation source parameter matching method in traditional signal processing methods. At present, the information available for real-time sorting of radar signals in electronic warfare systems is still the five major parameters of radar signals: carrier frequency (RF), pulse width (PW), direction of arrival (DOA), time of arrival (TOA), pulse amplitude (PA). Among them, RF is generally concentrated on several discrete frequency points with good convergence, so it is one of the most important features in reconnaissance signal processing; DOA depends on the relative azimuth of the radar and reconnaissance aircraft, when there is no relative azimuth between the radar and reconnaissance aircraft. When moving, the DOA is constant. When there is relative movement, the DOA changes slowly. This parameter is not affected by the radar signal itself. It is also one of the most important features in reconnaissance signal processing. Because the radar signal PW itself is relatively stable, the numerical value distribution is relatively concentrated. It has good stability and convergence, so it can also be used as one of the sorting characteristics; because there are too many factors affecting PA, the stability of PA is poor, and the reliability is not high, so it is generally not used as a basis for sorting; and TOA is generally used as the main sorting and identification parameter of the main processor, and generally not as a basis for pre-processing sorting. Therefore, theoretically speaking, there are 3 parameters available for preprocessing: RF, PW, and DOA.

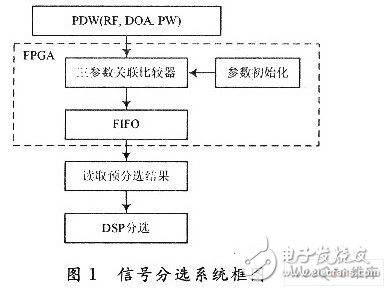

The block diagram of the sorting system is shown in Figure 1. The pulse sorting is divided into two parts: pre-sorting and main sorting. The pre-sorting is RF, PW, and DOA three-parameter joint sorting, which is completed by FPGA; the main sorting is heavy sorting. Frequency (PRI) sorting is done by DSP.

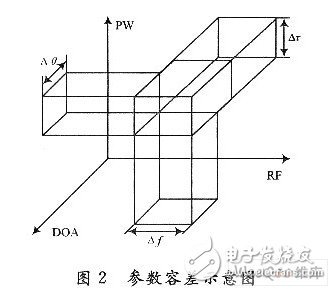

According to the principle of the three-parameter correlation comparator composed of RF, PW, and DOA, as shown in Figure 2. Each radar signal occupies a small box in space. The center coordinates of the small box can be considered as radar parameters. The size of the small box depends on the parameter tolerance, which is related to the measurement accuracy of the receiver. As long as the measurement reaches a certain accuracy and the appropriate tolerance range is selected, the pulses in this small box can be de-interleaved, and finally the existence of the pulse sequence can be determined.

Due to the diversity of radiation source characteristics and the introduction of pulse parameter measurement errors, the radar interception system pulse de-interlacing has the following two problems:

(1) Due to parameter jitter or measurement error, the parameter is a range defined by upper and lower thresholds.

(2) Due to parameter agility or parameter diversity, the parameters have multiple values ​​(such as frequency agility, diversity, etc.).

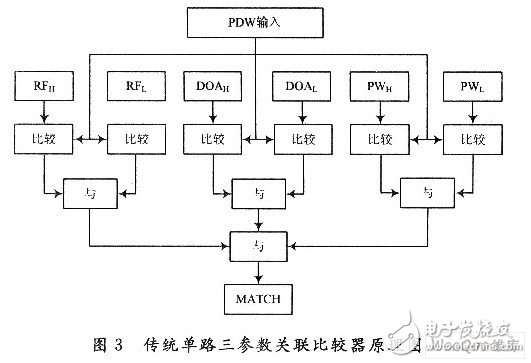

The schematic diagram of the traditional correlation comparator is shown in Figure 3. This method is to set a tolerance for each parameter, and compare the PDW of each pulse with the tolerance of each parameter. In fact, it is compared with RF, DOA, The maximum value and minimum value of PW are compared, and if they all fall within the tolerance range, the corresponding single-channel matching signal MATCH is generated. This method can solve the first problem, but it cannot be sorted for parameter agile radars. In addition, since each channel can only be configured with one set of radar parameters, this method is no longer suitable for the increasingly complex electromagnetic environment.

This paper improves on the traditional correlation comparator, and designs a correlation comparator based on CAM (Content-Addressable Memory). CAM is a memory specially designed for quickly finding data addresses. By comparing the input data with the data stored in it at the same time, it can quickly determine whether the input data matches a certain data or several data within it. The data addressing mode of CAM is different due to different application requirements. In the fastest mode, only one clock cycle is required to complete the addressing of all data.

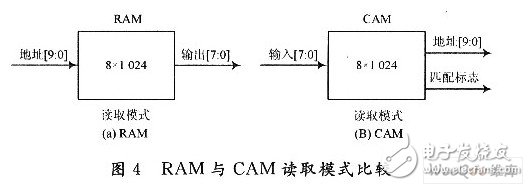

Like RAM, CAM also adopts array data storage, and its data writing method is similar to RAM, but the data reading method of CAM is different. In RAM, the input is the data address, the output is the data, and the input in the CAM is the data to be queried, and the output is the data address and matching flag.

In RAM, the storage capacity of RAM is determined by the width of the address line. For example, the RAM storage capacity of a 10b wide address bus is 210=1024B, but CAM does not have this limitation, because it does not use the traditional way of reading data by address. If you want to query a certain data from 1024B, the input data width is 8b. If the data exists, the matching flag and 10b wide data address will be output. Because the CAM does not use the traditional address line mode to read data, the storage space can be easily expanded, and the input data line width is only determined by the number of data bits to be queried. Figure 4 shows RAM and CAM in data read mode.

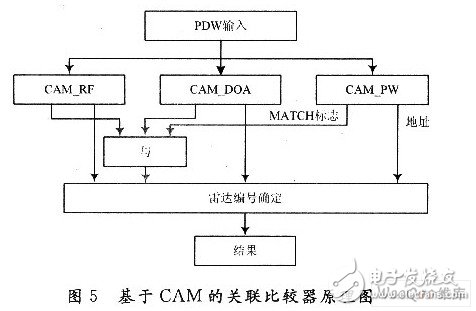

The principle of the CAM-based correlation comparator is shown in Figure 5. The RF, DOA, and PW parameters of multiple radars are stored in the three CAMs. When the PDW comes in, if there are matching parameters in the CAM, the MATCH flag will output 1, and the parameter address will be output, and the radiation source number will be determined according to the addresses of the three CAM outputs and the MATCH flag. Like the traditional method, this method can also be multiplexed to achieve high-speed processing of PDw.

The FPGA used in this article is XC4VSX55 ​​of Xilinx's Virtex 4 series. ISE 11.1 provides users with an IP core of CAM version 6.1, and its configuration interface is shown in Figure 6.

The CAM output address matching type has three configurations, the default is binary encoded, which means that the matched address information is output. In addition, it can also be configured as single-match unencoded and multi-match unencoded. The output of these two modes is a binary code with the same number of bits as the number of data in the CAM. The matching bit is 1, and the rest are 0. For example, there are 8 data in CAM, and the input data matches the third number, then 00100000 is output.

3.2 Three-state modeThe standard tri-state mode means that the content written to the CAM can be 1, O and X. X refers to the bits that are not concerned. The result of any value compared with X is considered to be a match. For example, the content that matches 10X1 is 1011. 1001. The enhanced three-state mode has one more U than the standard mode. U and X are just the opposite, which means that any value compared with U is considered to be a mismatch.

After analyzing the CAM core, the introduction of X in the tri-state mode can achieve one-to-many matching, so that a value in the CAM can not only correspond to multiple values ​​within the tolerance range, but also correspond to the middle parameter of the parameter agile radar Of multiple values. For example, the frequency parameter range of the radar is 01111100b≤RF≤01111111b, and it can be realized as long as the binary number 011111XX is pre-stored in the CAM. Using this principle, this article uses AcTIve-HDL 8.2 software to implement the design of the pre-sorter in FPGA.

The initialization data write to the CAM and RAM cells can be initialized in advance, or can be updated in real time during the working process of the system. In the application of radar signal pre-sorting, the known radiation source library can be initialized with the initialization memory file to CAM and RAM. The parameters of unknown radiation sources can be dynamically written in real time during the working process of the system.

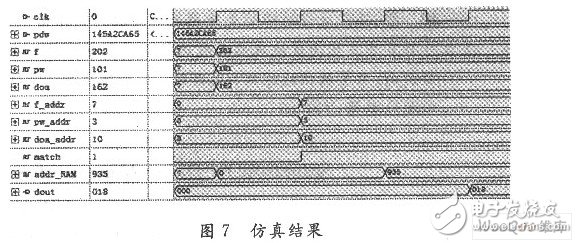

Figure 7 is a simulation diagram in AcTIve-HDL8.2. From the input PDW, you can get PW=101, DOA=162, RF=202. The three parameters are entered into the corresponding CAM to get the matching result and the matching flag, and finally get Matches the radar number 18.

The CAM-based correlation comparator is of great significance in radar signal pre-sorting, which can greatly increase the speed of signal sorting and save more time for back-end processing. In this system, an associated comparator based on CAM is designed in FPGA, which realizes the rapid pre-sorting of radar signals and meets the requirements of real-time and reliability.

Iget Legend,Iget Legend Pod Pen Kit,4000 Puffs Iget Legend Disposable Vape,Iget Legend E-Cigarette Australia

Shenzhen Uscool Technology Co., Ltd , https://www.uscoolvape.com