introduction

This article refers to the address: http://

The production of portable consumer electronics such as mobile phones, PDAs and MP3 players is usually very large. As a result, product design engineers will first choose to use AsIc or ASSP in a compact, portable package to accommodate the most powerful features.

This solution not only meets the requirements of functional intensiveness, but its power consumption is often satisfactory. However, in the context of the rapidly changing consumer electronics arena, vendors are committed to delivering differentiated solutions to changing technologies and markets, so time-critical features are outdated in a few months.

The word cruel is often used to describe the intensity of competition. Errors are neither intolerable nor costly, however, the choice of ASSP or the design of an ASIC is almost impossible to correct every time. Therefore, for manufacturers to ease this situation is crucial to maintain market share.

Today's design engineers are not only focusing on the unchanging ASIC and ASSP architecture, but also on the design flexibility inherent in programmable logic and the advantages of being available as soon as possible. Xilinx's CoolRunner-IICPLD offers low-cost and low-power advantages, providing portable device design engineers with a viable solution that can replace standard cell technology.

Since 2001, the CoolRunner-IICPLD family has been designed by design engineers at a price low enough to match the price of discrete logic devices, enabling design engineers to easily implement a wide range of logic functions in a single package. This article describes how to use CoolRunner-II CPLDs to implement low-cost and low-power simple programmable logic to overcome the limitations of today's ASIC/ASSP portable handheld solutions. Since most handheld devices are based on OMAP, Xscale or i.MX design, this article will address the resolution of several specific issues.

Level shifting

Providing an interface connection between chips of two different voltage standards is a common problem. No type of memory can meet all voltage standards, but the microprocessor can accommodate multiple voltages. Matching various standards is simple, using a level shifter; but level shifters are expensive and take up too much space. Using a CPLD is a better solution and can significantly increase flexibility. All CoolRunner-II CPLDs can convert between two voltages, while others can convert up to four voltages.

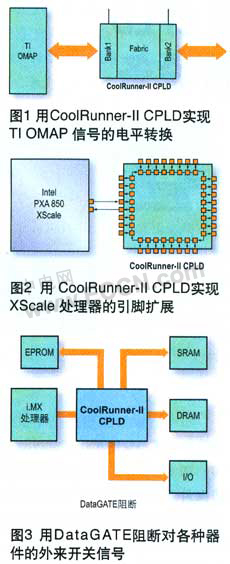

The CoolRunner-II CPLD's I/O group makes it easy to convert voltages from 1.5V to 3.6V in a single chip, as shown in Figure 1. But this is the case when the device programmability is not considered at all. The level shifting function is only part of the overall package, which means that the user can also get a batch of logic, flip-flops, power-down resources and I/O buffers, which are often lower than the price of the level shifter chip.

Pin extension

In general, the more ASIC pins, the higher the cost. If the logic requires a small amount of capacity and there is a large capacity requirement for I/O, then the engineer may have to buy logic that is not needed to meet the pin requirements. One way to solve this problem is to add a CoolRunner-II CPLD and use it as a pin expander, as shown in Figure 2.

The basic idea is to find the GPIO pins that normally run at low speeds. Instead of assigning ASIC pins to it, the CoolRunner-II CPLD pins are assigned to low-speed GPIO signals, these signals are serialized, and these signals are routed into the ASIC through fewer network pins. Serialization/deserialization is accomplished through simple and efficient shifting, which greatly reduces pins on high cost ASICs.

Another view is that OMAP, Xscale, and i.MX processors have specific pin combinations to support applications that the vendor deems appropriate. The CoolRunner-II CPLD pin extension allows engineers to create their own GPIO pins with different voltage combinations and additional functions (pulse, PWM, independent tri-state control).

Pin redistribution

CPLDs provide the ability to rearrange pins when an error occurs in the PCB layout. This feature is critical, allowing engineers to stay on track and meet financial and power budget requirements. Design engineers can correct their misconnections without having to redesign the board, so product schedules can be reduced by weeks to months.

CoolRunner-II CPLDs are built from powerful logic blocks in which programmable logic arrays can be arbitrarily redistributed. These devices can be modified to preserve the pin layout with multiple modifications, while reassigning the design to different pins as needed. The CoolRunner-II family of data sheets provides an architectural description and an application guide index that details the application's understanding of the value of the PLA.

Power Control

Fast power-on is one of the advantages of CPLD. The CoolRunner-II CPLD comes with a configuration unit that allows it to power itself and guide subsequent activities of other chips. This includes some power conditioners (sequenced by the CoolRunner-II CPLD) and other control signals that need to be properly defined in advance in board operation.

Reduce power consumption

All XScale, OMAP and i.Mx based chipsets include some version of the ARM microprocessor. Advanced RISC machines were originally developed in a way that runs microprocessors at low power. Later, each license vendor adopted its own method to further reduce processor power consumption. Typical power-down operations include clock gating, voltage scaling, and on-board memory management designed to reduce intra-device transfers.

In addition, operating systems such as Symbian have added a "power-aware" mode to various power-saving methods to keep unused resources as low as possible in the lowest power mode of the task currently being performed. These methods work well and both reduce the power consumption of the processor. However, reducing the power consumption of the rest of the system is beyond the scope of these methods.

CoolRunner-II CPLDs are inherently low power devices. More importantly, the special features of CoolRunner-II can also be used to reduce the power consumption of other devices. Using the clock divider and Xilinx DataGATE technology can reduce the power consumption of many, if not all, of the chips in the design, as shown in Figure 3. Turning off power to other chips can also reduce electromagnetic fields that propagate on the board and emanate from the system. This effective signal blocking method has many advantages.

Logical merge

Installing three 2-input gates, two three-input gates, and a Schmitt buffer package on the board increases bill of materials (BOM), power consumption, and cost budget, and reduces reliability. If you put these scattered logic into an overall low-power CoolRunner-II, you can not only solve these problems, but also store other unused logic directly on the board for future improvements/modifications. Table 1 lists the resource consumption rates for the logic.

in conclusion

CoolRunner-II CPLDs are rapidly becoming the standard for low-power, low-cost, high-volume portable consumer products. This article focuses on how this powerful product makes it easy to build systems using OMAP, Xscale, and i.MX processors. CoolRunner-IICPLD is equally effective for many other processors, adding functionality, reducing power consumption, and reducing time to market.

Shenzhen Ruidian Technology CO., Ltd , https://www.wisonens.com