Julian Hagedorn

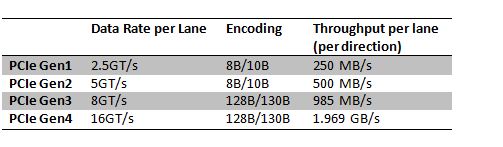

PCI Express® (PCIe®) is an industry-leading standard input/output (I/O) technology and one of the most commonly used I/O interfaces in servers, personal computers, and other applications. The standard has evolved over the years to accommodate higher data rates (see Table 1). Generation 3 PCIe introduces a new encoding scheme that doubles data throughput without increasing the data rate by a factor of two. PCI-SIG's recently announced 4th generation PCIe has a 16 Gbit/s transfer rate (GT/s) bit rate. The 4th generation specification is expected to be released in 2014 or 2015.

Table 1: Data throughput for each generation of PCIe

With the increase of data rate, the demand for reference clock is also increasing. This article will focus on reference clock requirements.

The PCIe Reference Clock (RefClk) specification can be defined for 3 different architectures: Data Clock, Independent RefClk, and Generic RefClk. Each architecture has a specific filter function. The effective jitter that occurs at the receiver clock data recovery input is a function of the difference between the receiver and transmitter PLL bandwidth and the peaks involved in the RefClk jitter spectrum. In addition, it also depends on the RefClk architecture.

In the standalone RefClk architecture, both the transmitter (TX) and the receiver (RX) can receive independent RefClk. This leads to strict jitter requirements and cannot apply Spread Spectrum Clock (SSC).

In the data clock architecture, a single RefClk can be connected to the transmitter while the receiver uses the embedded clock signal from the data stream. The clock data recovery (CDR) circuit can extract the clock in the data stream. It minimizes the jitter requirements and also applies SSC. However, this is a relatively new standard and many devices do not support it.

The best candidate standard (and the most commonly used standard) is the generic RefClk architecture. It not only provides the same RefClk to the transmitter and receiver, but also supports SSC that reduces electromagnetic interference (EMI), which is very easy to implement. The disadvantage of this architecture is that RefClk needs to meet the offset requirement of less than 12ns. The following is a generic RefClk architecture and its application examples.

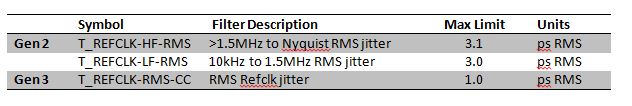

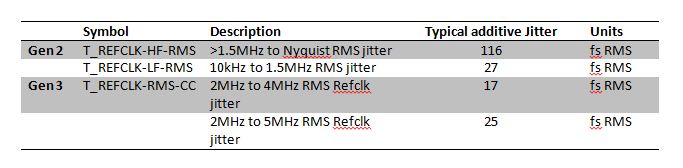

Table 2: Generic RefClk Jitter Specifications After Applying Filter Functions

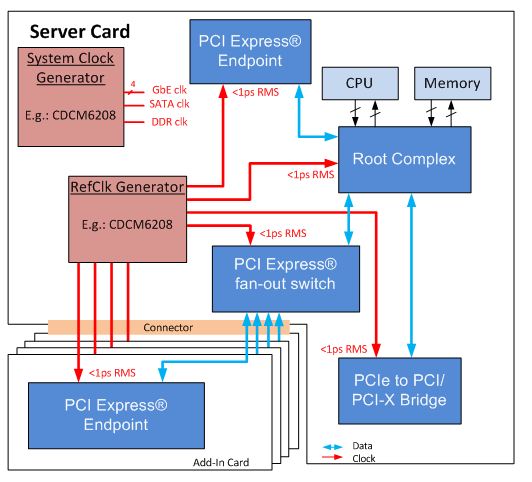

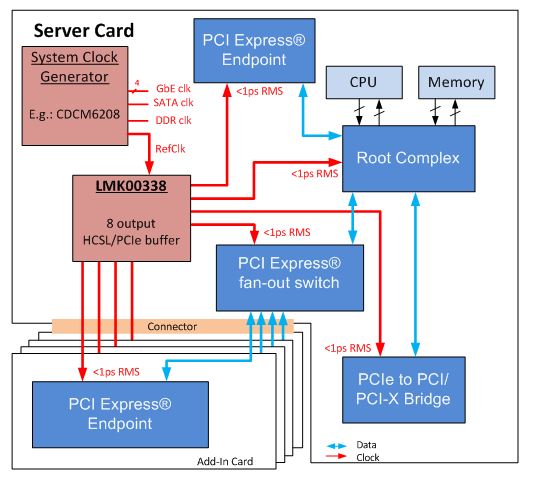

Common PCIe applications such as server cards include several building blocks. The heart of the system is the root complex, which represents the root of the I/O system. The root complex connects the CPU and memory and may have multiple PCIe ports. In addition, it also includes switches and PCIe endpoints such as video cards. All components of the I/O system must meet the jitter requirements of the transmitter/receiver and RefClk. If all building blocks are compatible with PCIe Gen 3, then RefClk requirements of 1 ps rms are required (Figure 1).

Figure 1: Solution 1: Server card instance supporting Gen 3 PCIe Generic RefClk Jitter throttling

The system shown in Figure 1 can be implemented using a 7-output clock generator. This implementation may eventually require more than one clock generator-based clock tree solution because other system clocks need to be generated as well. The system clock generator generates reference clocks for Gigabit Ethernet devices, SATA controllers, DDR clocks, and so on. In Figure 2, the RefClk generator is replaced by a clock buffer. This not only simplifies the clock tree but also provides a lower cost, more space-optimized solution.

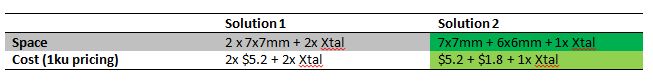

Table 3: Comparison between Solution 1 and Solution 2 and Space and Cost

Figure 2: Solution 2: Server card instance using RefClk buffer such as LMK00338

When buffer allocation RefClk is used, the additional jitter caused by the buffer needs to be considered. The definition of additive jitter is the amount of additional jitter that the device itself generates for the input signal. The calculation method is: ![]() .

.

Assume that the noise process is random and the input noise is independent of the output noise. The jitter output of the buffer can be calculated by this formula: ![]() .

.

The LMK00338 is an ultra-low additive jitter PCIe clock buffer. For 3rd generation PCIe applications, there is typically 30 fs rms additional jitter. Table 3 shows the additional jitter performance when using different PCIe filter functions.

Table 4: Additional jitter performance of the LMK00338

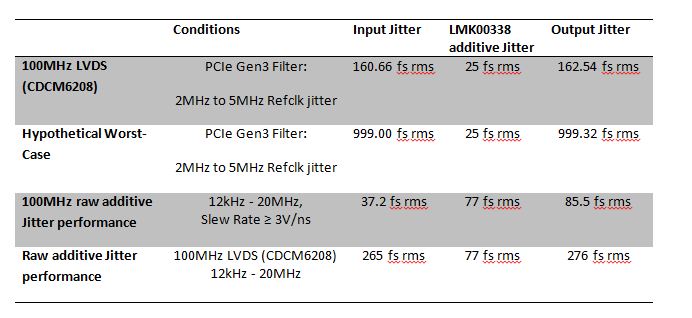

The 3rd generation PCIe high performance clock generators such as the CDCM6208 provide RefClk with 160.66fs rms jitter (2MHz to 5MHz filter). If this clock is allocated, the LMK00338 adds 25 fs rms jitter to the RefClk signal. The output jitter calculated using the above formula is only 162.54 fs rms (Table 5). In the worst case, the RefClk generator may have jitter of 999fs rms and using the LMK00338 will not exceed the Gen 3 PCIe jitter limit.

Table 5 shows the additional jitter performance of the LMK00338 when the PCIe filter function is not applied. With low additive jitter of 77 fs rms (integrated bandwidth: 12 kHz to 20 MHz), this buffer is suitable for most high-performance clock applications that use HCSL signal transmission technology. There is also a smaller 4-output version.

Table 5: Effect of a low jitter RefClk source (CDCM6208) driven clock buffer.

A common problem in multiple server cards is power supply noise issues. Noise can come from multiple noise sources, first switching power supplies, and digital circuits such as CPUs, ASICs, or FPGAs. Power bypassing will help filter out some of the noise, and the remaining noise will affect device performance. When residual noise affects the power supply of the clock distribution device, it results in narrowband phase modulation and amplitude modulation of the clock output.

In the noise frequency range of 100kHz to 10MHz, the LMK00338 can exhibit excellent PSRR (Power Line Ripple Suppression) performance below -75dBc at 100MHz output frequency. This noise immunity will help simplify power supply bypassing, another important advantage of the LMK00338.

The above analysis shows that as long as the RefClk generator meets the jitter requirements, it is safe to use the ultra-low additive jitter clock buffer in a generic RefClk system.

In addition, the LMK00338's universal input stage accepts not only any differential or single-ended signals, but it can also be converted to 8 HCSL outputs. For Generation 4 PCIe, the maximum RefClk jitter can be assumed to be much less than 1ps rms. Therefore, a generic RefClk architecture that supports buffering will be better suited to the more stringent newer PCIe standards.

Aluminum Electrolytic Capacitors

Aluminum Electrolytic Capacitors

Large Electrolytic Capacitor,HV Electrolytic Capacitors,Aluminum Electrolytic Capacitors

YANGZHOU POSITIONING TECH CO., LTD. , https://www.pst-thyristor.com